Welcome to DVCon Japan 2025 !

2025年8月20日 @ TKPガーデンシティPREMIUM品川高輪口

Design & Verification Conference & Exhibitionは、電子システムおよび集積回路の設計と検証のための言語、ツール、メソドロジ、標準の適用に関する最高峰のカンファレンスです。このカンファレンスは非常に技術的なコンテンツで構成され、設計と検証の技術の実用的な側面や、最先端プロジェクトにおける活用に焦点を当てています。参加者が同様の技術を参考にしたり採用したりすることで、自身の設計や検証のフローの改善が促進され、ひいては業界全体の技術水準が高まることを目指しています。

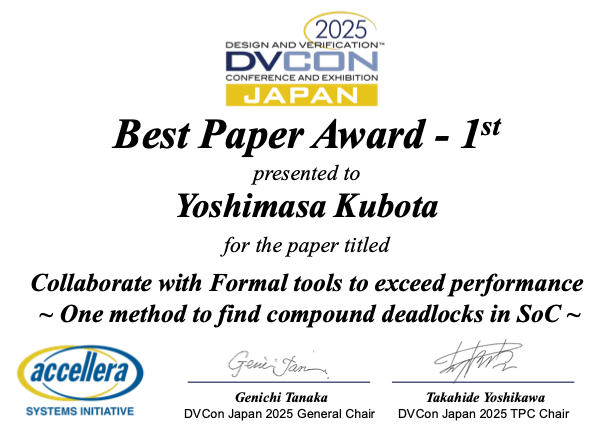

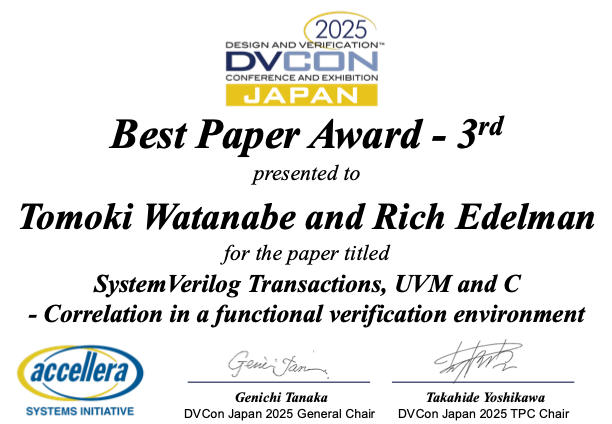

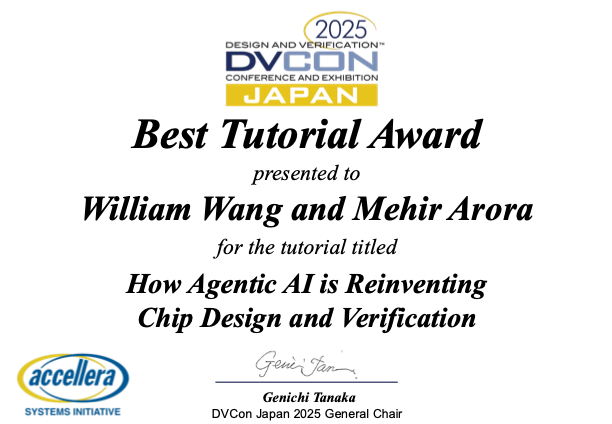

Best Paper Award and Best Tutorial Award

Congratulations to all authors and presenters !

Accelleraチェアからのメッセージ

Gold Sponsors

Silver Sponsors

Exhibitor

Supporters

Media Sponsors

ごあいさつ

皆さん、こんにちは。

来る2025年8月20日、品川にて、DVCon Japan 2025を開催いたします。

DVCon (Design and Verification Conference)はAccellera Systems Initiativeがメインスポンサーとなって開催されるカンファレンスです。半導体やシステムにおける論理設計やアーキテクチャ検討、機能検証、HW/SW協調検証、アナログシミュレーション、機能安全準拠やセキュリティ検証、AIの開発フロー適用など、幅広い分野における課題解決に注力しています。IEEE標準やAccellera標準の言語、フォーマット、メソドロジなどの適用におけるベストプラクティスついて学び、議論するカンファレンスです。

DVConは米国において30年以上の歴史があり、日本国内においては2022年から国内開催しています。2022年はオンライン配信とオンデマンド配信での開催でしたが、2023年、2024年には対面で開催いたしました。さまざまな論文発表やチュートリアルセッション、スポンサーや出展者による展示によって、多彩かつ深い内容をお届けすることができました。聴講者、発表者、スポンサー、関係者の皆様に感謝を申し上げます。

DVCon Japan 2025は、品川駅の高輪口から徒歩3分でアクセスが可能な会場で開催いたします。午前中はジェネラルセッションやパネルディスカッション、午後は多くの論文発表やチュートリアルなどのテクニカルセッションで構成する予定です。同時にスポンサーや出展企業や協会による展示も開催いたします。DVConは機能検証戦略、SystemVerilogやUVM、UPF、SystemC、PSS、フォーマル検証メソドロジ、HLS、AMS、IP-XACTなど、多岐にわたる分野における最新の情報を共有し、そして議論をする場です。また参加者どうし、発表者と参加者、スポンサー、さらにはAccellera代表者らとの交流を深める場としてもご活用いただけます。

設計者、技術者、そして管理者の方々に、積極的にご参加いただきますよう、お願い申し上げます。会場で皆様とお会いできるのを楽しみにしています。最後に開催を支援いただいているスポンサーの皆様、そして協賛いただいている情報処理学会、IEEE CEDA AJJC、電子情報通信学会の方々に、この場をお借りしまして厚く御礼申し上げます。

EXAMPLE TOPICS

▼ Verification and Validation

・最新の検証メソドロジやテストベンチ

・検証プロセス、リグレッションテストやリソースマネジメント

・複雑なデザインにおけるデバッグや解析手法

・複数言語を用いた設計と検証

・組込みシステムにおけるハードウェア/ソフトウェアの協調設計と協調検証

▼ Design and Verification Reuse / Automation

・複数の検証エンジンをまたぐ検証やバリデーションの接続性・整合性

・SoCとIP統合の手法

・AccelleraのPSS (Portable Test & Stimulus Standard)標準の適用

・IPのコンフィギュレーション管理と抽象度

・ESL言語からの高位合成や高位検証

・仮想プロトタイプ、シミュレーション、エミュレーション、FPGAプロトタイプ間の接続性・整合性

▼ Machine Learning and Big Data

・検証プロセスの最適化とその自動化

・カバレッジ指標とビッグデータ解析

・パフォーマンスのモデリングおよび解析

▼ Low-Power Design and Verification

・低消費電力設計とその検証

・クロックドメイン・クロッシングの検証

・消費電力のモデリング、見積もりと消費電力管理

▼ Safety-Critical Design and Verification

・DO-254遵守と検証

・ISO 26262における設計と検証のチャレンジ

・医療機器や工業機器における検証のチャレンジ

・要件駆動型 (Requiremenets-Driven) の検証メソドロジ

・IPの知的財産保護とセキュリティ

▼ Mixed-Signal Design and Verification

・ミクストシグナルの設計と検証テクニック

・実数 (Real Number) モデリングのアプローチ

・ミクストシグナルのUVM拡張と適用

CONFERENCE SPONSOR

Accellera Global Sponsors

Academy Sponsors